- cross-posted to:

- technology@lemmy.ml

- cross-posted to:

- technology@lemmy.ml

Eh. LPCAMM seems more useful overall as a product. Faster DDR at this point in time has diminishing returns.

It’ll be interesting to see how this plays out though, because there are a few different paths to solve this type of problem with DDR5. Personally, I’d love for much lower power, but a wider bus, which is where I thought things were heading.

Well usually yes, but if cpu manufacturers decide to really lean into cramming lots of cores into cpu-s (Like Intel’s big.LITTLE cpus, but even more cores), then we probably will need faster RAM-s, since more core == more memory bandwith demand, and currently this issue has been always resolved by faster RAMs. (Or we could just increase the memory channels)

LPCAMM may have better specs, but DIMM requires a smaller area on the PCB and can make better use of the vertical space.

These are unrelated products. Not sure what you mean.

LPCAMM seems more useful overall as a product.

Only if you need 2-4 sticks, otherwise they take up too much PCB space. Look at servers and how a good chunk of their volume is filled with dozens of sticks. You cant simply lay them down flat.

Well we’ve seen CAS latency increase almost quicker than DDR speeds. CAMM should address this issue by shortening the distance from cpu to RAM, at least for laptops.

I’d say DIMM has pretty much stranded in DDR5.

faster ram generally has dimishing returns on sustem use, however it does matter for gpu compute reasons on igpu (e. g gaming, and ML/AI would make use of the increased memory bandwith).

its not easily to simply just push a wider bus because memory bus size more or less affects design complexity, thus cost. its cheaper to push memory clocks than design a die with a wider bus.

Computational-Fluid-Dynamics simulations are RAM-limited, iirc.

I’m presuming many AI models are, too, since some of them require stupendous amounts of RAM, which no non-server machine would have.

“diminishing returns” is what Intel’s “beloved” Celeron garbage was pushing.

When I ran Memtest86+ ( or the other version, don’t remember ), & saw how insanely slow RAM was, compared with L2 or L3 cache, & then discovered how incredible the machine-upgrade going from SATA to NVMe was…

Get the fastest NVMe & RAM you can: it puts your CPU where it should have been, all along, and that difference between a “normal” build vs an effective build is the misframing the whole industry has been establishing, for decades.

_ /\ _

Why does desktop hardware become more and more complex and fragile?

I want my BunkerNet with 90s Amiga level machines with technology practical enough to be produced (with reasonable investment) at least in every 1mln city (with literate population and necessary raw resources available).

Yes, I’ve even started with something above that, running Windows 98SE, games and all.

But just … how necessary it really is? Just (that is, 1.5 hrs ago, ADHD) returned home from a bicycle ride in a park, it’s fun with a normal bicycle, it’s fun with a Soviet bicycle which is barely that, it’s fun with a foldable bicycle with switchable reductors, it’s fun with roller skates, and it’s fun on foot.

Can we treat computers the same? They are means to an end. NEW ROUNDED CORNERS AND ADS IN EVERY ORIFICE TO BE ALWAYS CONNECTED TO OUR NEW ARTIFICIAL INTELLIGENCE is not that end.

EDIT: ok, each 1mln city is asinine ; each 5-10mln people on the planet maybe?

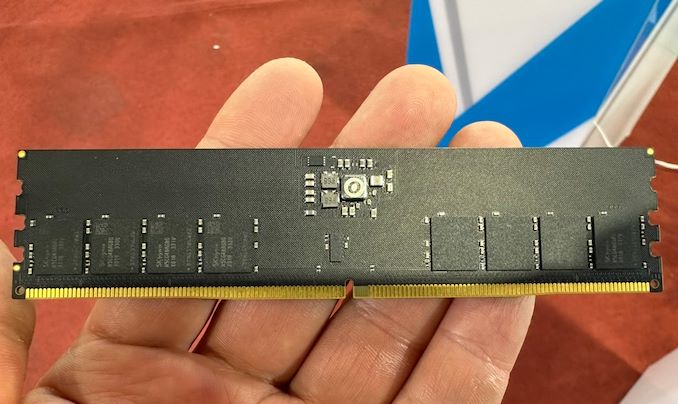

Standardized by JEDEC earlier this year as JESD323, CUDIMMs tweak the traditional unbuffered DIMM by adding a clock driver (CKD) to the DIMM itself, with the tiny IC responsible for regenerating the clock signal driving the actual memory chips. By generating a clean clock locally on the DIMM (rather than directly using the clock from the CPU, as is the case today), CUDIMMs are designed to offer improved stability and reliability at high memory speeds, combating the electrical issues that would otherwise cause reliability issues at faster memory speeds. In other words, adding a clock driver is the key to keeping DDR5 operating reliably at high clockspeeds.